# Al for Fully-Automated Chip Design: The Times They Are a-Changin'

Institute of Computing Technology, Chinese Academy of Sciences

Xing Hu

#### 2024: Gimmick or Trend

Al for Automated Chip Design: Everything, Everywhere, All at Once (?)

David Pan, The University of Texas at Austin

Automatically generating robotics accelerators

Yuhao Zhu, University of Rochester

Break

A Systematic and rapid approach to design space exploration for tensor accelerators Qijing Huang, NVIDIA

Empowering Physical Design of VLSI Circuits with Deep Learning: from Modeling to Optimization

Yibo Lin, Peking University

Machine Learning for System-Level Design: Challenges and Opportunities

Andreas Gerstlauer, The University of Texas at Austin

Chip Learning for Processor Design

Zidong Du, Institute of Computing Technology, Chinese Academy of Sciences

Scaling Up the Hardware Design Capability of LLMs: Lessons from the 1st OpenDACs Contest of Processor Design

Cangyuan Li, Institute of Computing Technology, Chinese Academy of Sciences

A High-Level Synthesis Based Framework for Design Space Exploration and Generation of Neural Network Accelerators

Kartik Prabhu, Stanford University

Machine Learning Assisted Memory and Storage System Management

Onur Mutlu, ETH Zurich

#### 2025: The Times They Are a-Changin'

Hypothesizing (Fantasizing) Autonomous Hardware Design Zhiru Zhang, Cornell University

The Role of AI for Next Generation SW/HW Codesign

Vincent T. Lee, Meta

QiMeng: Automated Hardware and Software Design for Processor Chip

Di Huang, Institute of Computing Technology, Chinese Academy of Sciences

Hair of the Dog: How Al Can Help Formally Verify Al-Designed Chips

Yatin Manerkar, University of Michigan

Learning with Limited Resources: Optimizing Neural Networks for Extreme Efficiency

Radu Marculescu, University of Texas at Austin

Break

hdl2v: A Code Translation Dataset for Enhanced LLM Verilog Generation

Towards an Agile and Autonomous Verification Framework for Al-Generated Chip Designs

Leveraging Large Language Models for Coverage-Driven Verification of Open-Source RISC-V Cores

ProtocolLLM: RTL Benchmark for SystemVerilog Generation of Communication Protocols

ChiseLLM: Unleashing the Power of Reasoning LLMs for Chisel Agile Hardware Development

# The Breakout Year for Reasoning Models

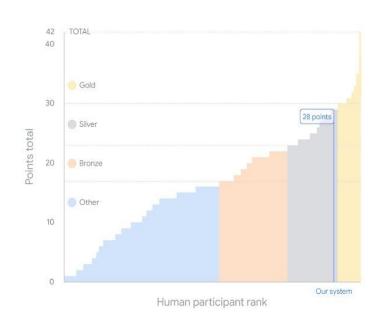

AlphaProof winning a silver medal at the IMO 2024

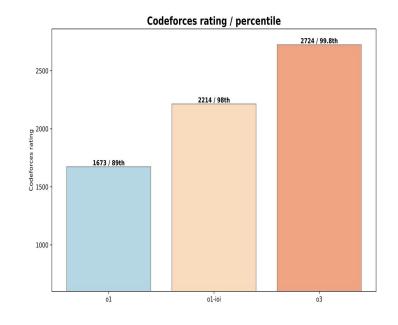

O3 achieved Gold; 99.8th in Codeforces

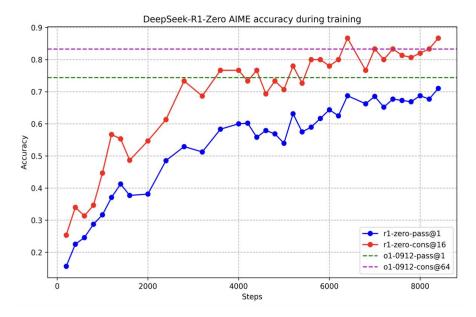

DeepSeek R1: Self-emergence of reasoning

# Processor Design: Apex of Logic Reasoning

R. Floyd

Automatic program

synthesis and

verification

J. Hopcroft

Logic synthesis

J. Cocke Circuit design

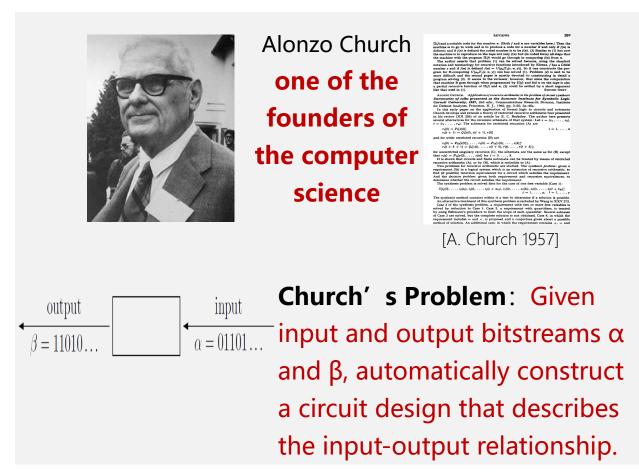

1957: The Church's problem of automatic circuit design

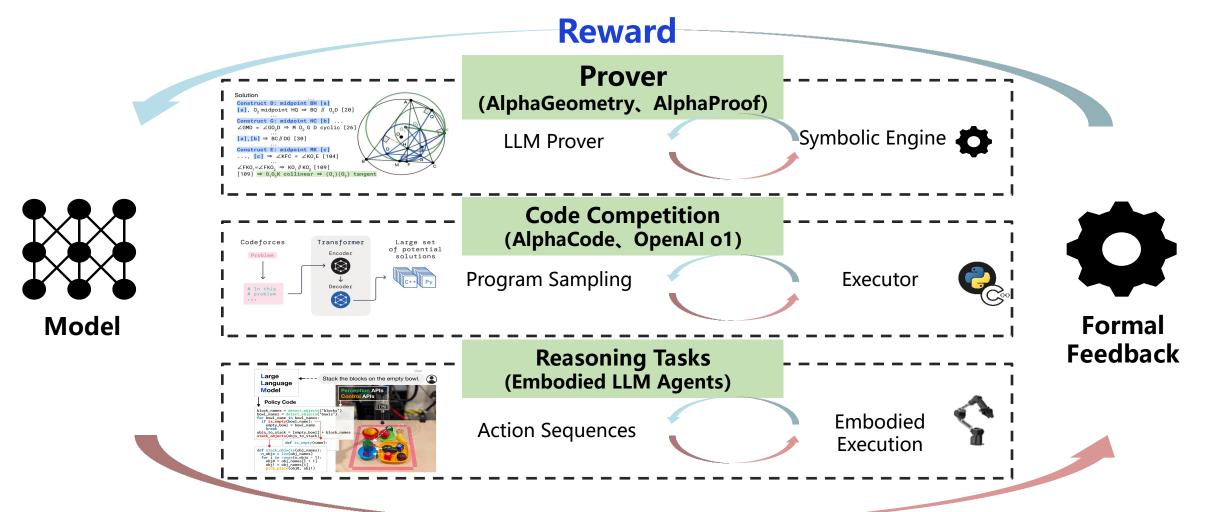

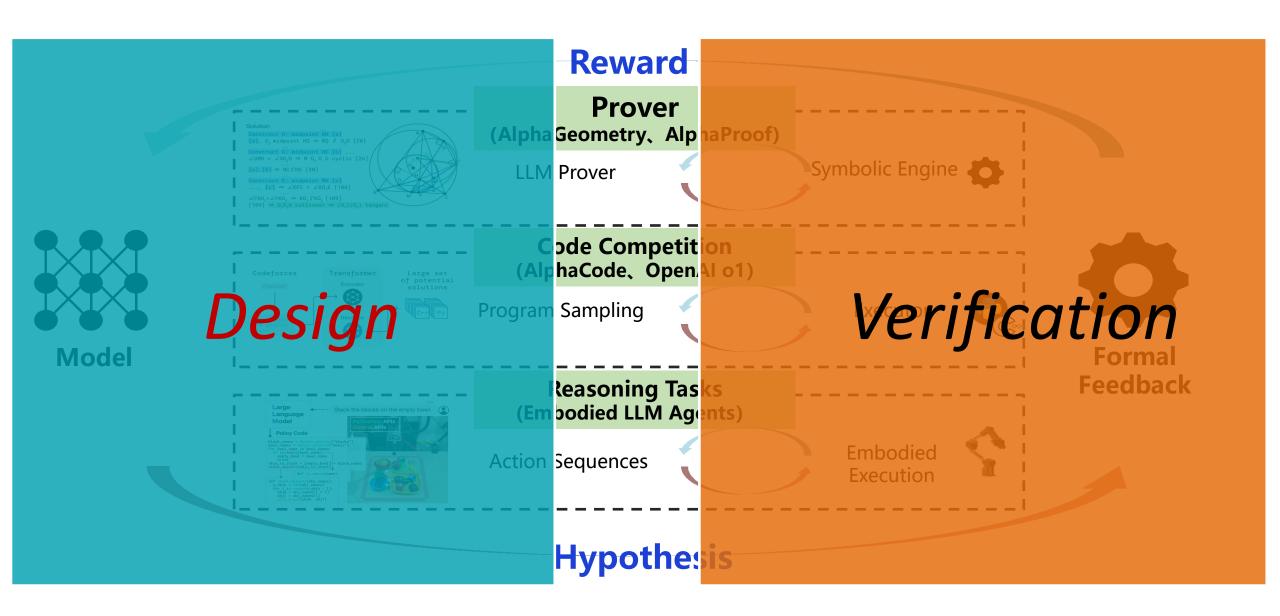

# Pradigm of Reasoning Tasks

**Hypothesis**

# Pradigm of Reasoning Tasks

#### Talk Overview

#### SW/HW Co-design

The Role of AI for Next Generation SW/HW Codesign

## Design

ProtocolLLM: RTL Benchmark for SystemVerilog Generation of Communication Protocols

ChiseLLM: Unleashing the Power of Reasoning LLMs for Chisel Agile Hardware Development

### Feedback-driven Loop

Hypothesizing (Fantasizing) Autonomous Hardware Design

QiMeng: Automated Hardware and Software Design for Processor

Chip

## **Verification**

Hair of the Dog: How AI Can Help Formally Verify AI-Designed Chips

Leveraging Large Language Models for Coverage-Driven Verification of Open-Source RISC-V Cores

**Boosting**

Boosting

## Data, Infrastructure, Tools

hdl2v: A Code Translation Dataset for Enhanced LLM Verilog Generation Learning with Limited Resources: Towards an Agile and Autonomous

Optimizing Neural Networks for Verification Framework for AI-Generated

Extreme Efficiency

Chip Designs